SR Latch (ungated)

A SR latch is used to store one bit of data. It is an example of a sequential logic circuit. The type of SR latch described here is an ungated SR latch which is asynchronous, that is to say, the data is stored as soon as the data input is changed. These differ from the gated type which are synchronous, that is to say, the data is stored when a control input is activated.

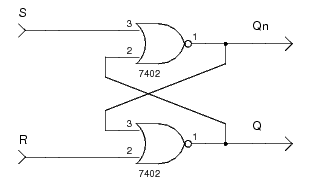

The schematic below shows an ungated SR latch.

The two inputs S and R are used to set and reset the data respectively.

The outputs Q and Qn are the stored data and the complement of the stored data respectively.

Example

The following function table shows the operation of an ungated SR latch.

S |

R |

Q |

Qn |

Meaning |

|---|---|---|---|---|

0 | 0 | Q | Qn | Hold |

0 | 1 | 0 | 1 | Reset |

1 | 0 | 1 | 0 | Set |

1 | 1 | 0 | 0 | Undefined |

Verilog

Below is the Verilog code for a structural model of an ungated SR latch.

module sr_latch_ungated(Q, Qn, S, R);

output Q;

output Qn;

input S;

input R;

nor(Qn, S, Q);

nor(Q, R, Qn);

endmodule

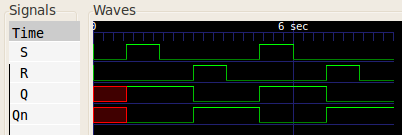

A simulation with test inputs gave the following wave form:

References

Kleitz, W. Digital Microprocessor Fundamentals. 3rd Edition. Prentice Hall, 2000.

Mano, M. Morris, and Kime, Charles R. Logic and Computer Design Fundamentals. 2nd Edition. Prentice Hall, 2000.