AND Gate

An AND gate is a fundamental binary logic gate with N inputs and one output. The output is 1 if all inputs are 1.

The equivalent logical connective is conjunction.

The following truth table gives the specification for a two input AND gate with output X:

A | B | X |

|---|---|---|

0 | 0 | 0 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

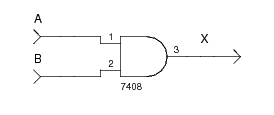

The schematic form of the AND gate is:

Below is a Verilog structural model for the AND gate.

In the code, the first argument to and is the gate output, the other arguments are inputs.

module and_gate(X, A, B);

output X;

input A;

input B;

and(X, A, B);

endmodule

References

Mano, M. Morris, and Kime, Charles R. Logic and Computer Design Fundamentals. 2nd Edition. Prentice Hall, 2000.

Kleitz, W. Digital Microprocessor Fundamentals. 3rd Edition. Prentice Hall, 2000.