ROM

ROM is Read Only Memory. Memory has size which is the number of memory locations, and width which is the number of bits used to represent the data at each memory location.

Verilog

Below is a Verilog dataflow model for an 8-bit wide ROM which contains a program for the 8085 microprocessor.

module rom (data, addr, en);

output [7:0] data;

input en;

input [7:0] addr;

wire [7:0] odata;

assign odata = (addr == 16'h0000) ? 8'hdb /* IN 0 */

: (addr == 16'h0001) ? 8'h00

: (addr == 16'h0002) ? 8'h2f /* CMA */

: (addr == 16'h0003) ? 8'hd3 /* OUT 1 */

: (addr == 16'h0004) ? 8'h01

: (addr == 16'h0005) ? 8'hc3 /* JMP 0000 */

: (addr == 16'h0006) ? 8'h00

: (addr == 16'h0007) ? 8'h00

: 8'h00; /* NOP */

assign data = en ? odata : 8'bz;

endmodule

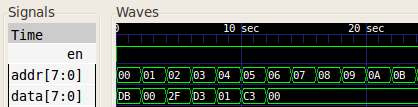

The following waveform shows a series of reads for addresses 0 through to 7 and beyond.